Package Reliability

Packaging and interconnection technology deals with the reliability of power electronic components and systems with special consideration of effects caused by the integration of the semiconductor chip into the particular package.

Power Cycling

In application, power electronic systems are exposed to a wide variety of load profiles, which can cause irreversible effects. Depending on the selected application, such changes can only become noticeable after a considerable load period. Accelerated aging tests are used to investigate the effects of certain test parameters on the packaging and interconnection technology of a power semiconductor package to a reasonable extent. Based on the test parameters, which are derived from the corresponding application, quantitative and qualitative statements on the effects of innovations can ultimately be made with the help of life cycle models and continuously measured sensitive parameters.

|

There are numerous aspects to be considered when power cycling in order to achieve a high degree of reliability, reproducibility and thus comparability. These include these aspects:

A matured hardware and software backup concept also allows almost autonomous operation. |

|

As different as the various power devices, their power classes and housing technologies are, so flexible must the test benches be.

Accordingly, the Chair of Power Electronics has a wide range of different test benches, which have grown over the years and ultimately

specialized for certain device groups and current classes. |

|

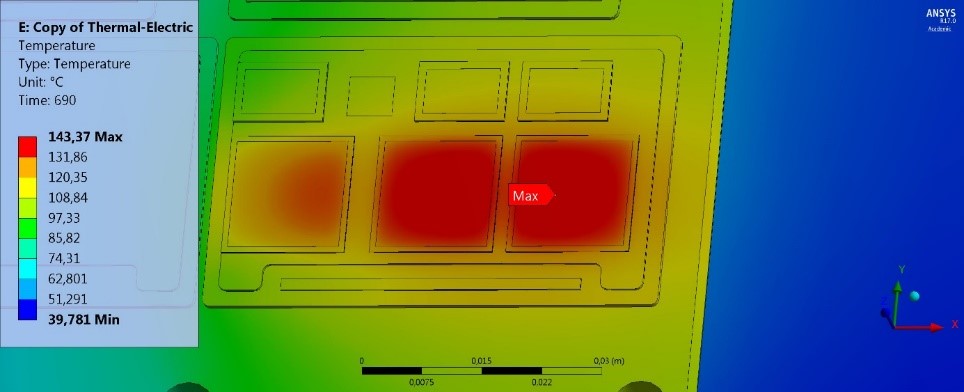

FEM Calculations

To determine the electrical, thermal and mechanical behaviour of power electronic devices with complex structures, systems consisting of

differential equations are being solved and analysed through numerical methods.

The progressive development of semiconductor elements is requiring an increasingly accurate insight into power electronics systems, to examine the

stress on single system components depending on electrical, thermal and mechanical parameters regarding increasing power density and efficiency.

Empirical data gained in various measurements using different assembly and connection techniques and material combinations, allows the valuation of numerical

determined results with regard to potential weak points in the system and explanation of associated failure pictures.

|