Dipl.-Ing. Andreas Käberlein

Dipl.-Ing. Andreas Käberlein

danach Entwicklungsingenieur bei Siemens AG Chemnitz

Arbeitsgebiete

- Forschung:

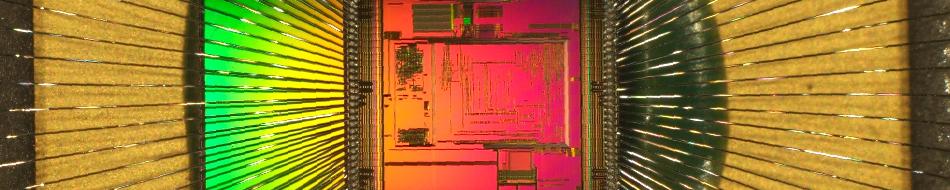

- Analog/Mixed-Signal-IC-Design (System, Schaltung, Layout)

- Digital-Design für ASIC und FPGA

- Lehre:

- Übung "Elektronische Bauelemente"

- Mitarbeit an Praktika "Elektronische Bauelemente und Schaltungen", "Integrierte analoge Schaltungstechnik", "Integrated Circuit Design - Transistor Level" und "Komplexpraktikum Mikroelektronik"

Veröffentlichungen

- Hofmann, A.; Käberlein, A.; Kögel, E.; Ramsbeck, M.; Horstmann, J. T.: A 12-bit SAR ADC in 180 nm Technology for Smart Sensor Systems, 2021 Smart Systems Integration (SSI), 27-29 April 2021, DOI: 10.1109/SSI52265.2021.9466967

- Lerner, R.; Käberlein, A.; Ramsbeck, M.; Beyer, D.; Berger, H.; Holzhey, R. Büttner, U.; Schrön, A.; Zimmet, J.; Volk, M.: Alternative level shifting devices for 900V gate drivers, 13th International Seminar on Power Semiconductors (ISPS'16), Prague, 31 August - 2 September 2016

- Lerner, R.; Schottmann, K.; Hering, S.; Käberlein, A.; Fritzsch, M.; Schneider, K.; Beyer, D.; Heinz, S.: Comparison of different device concepts to increase the operating voltage of a trench isolated SOI technology to above 900V, Facta Universitatis, Series: Electronics and Energetics Vol 28, No 4 (2015), ISSN 0353-3670, doi:10.2298/FUEE1504645L

- Lerner, R.; Schottmann, K.; Hering, S.; Käberlein, A.; Fritzsch, M.; Schneider, K.; Beyer, D.; Heinz, S.: Using SOI capabilities to increase breakdown voltages from > 650 V to > 900 V, 12th international Seminar on Power Semiconductors, ISPS 2014, Prague, 27-29 August 2014, ISBN 978-80-01-05555-7